# **MPS** Professional Audio power solution

HR1210 Digital PFC&LLC Controller+Flyback HF500-X

2020.12.28

### **Professional audio power**

# **Professional audio power**

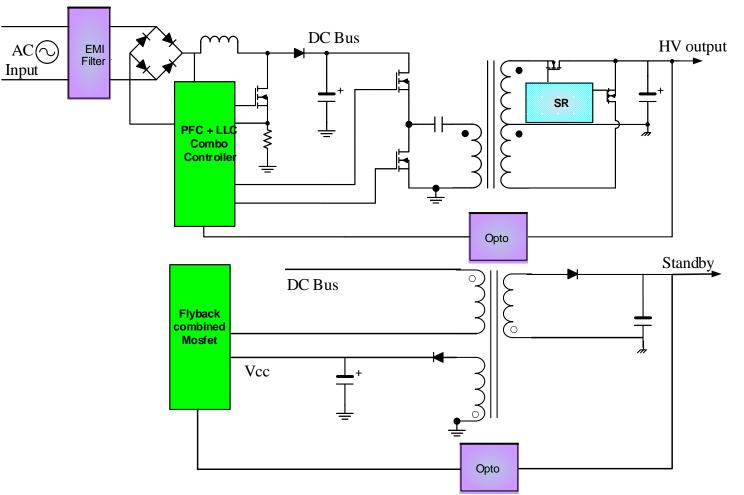

#### **Block diagram:**

#### **Powe spec:**

- Peak power up to 1kW,standby within 20W

- Load transient speed is fast with ms level and frequently

- > HV output have large cap, usually

>1500uF

**AC-DC solution need:**

- High power density and efficiency

- High reliability but easy to design

- Full protection feature

#### **MPS total solution:**

- > HR1210: PFC+LLC combin controller

- > HF500-X: Flyback combined Mosfet

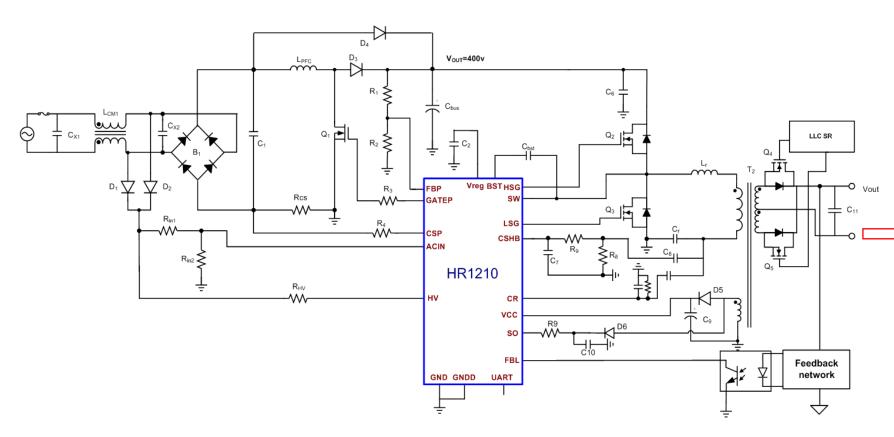

# **HR1210 Typical Application**

#### CCM/DCM PFC + Current Mode LLC

•SOIC-20 & TSSOP-20 •Full Digital Solution •CCM/DCM of PFC • Current/Voltage Mode LLC

#### HR1210

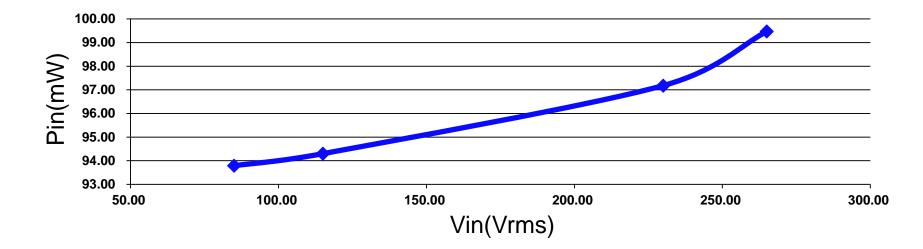

- Ultra-low no load power loss (Pin<100mW @ No Load)

- Improved and accurate burst mode control

- (n>80%@Pout=8W)

- UART Interface

- GUI for design (Both PFC & LLC)

# **HR1210 Typical Application**

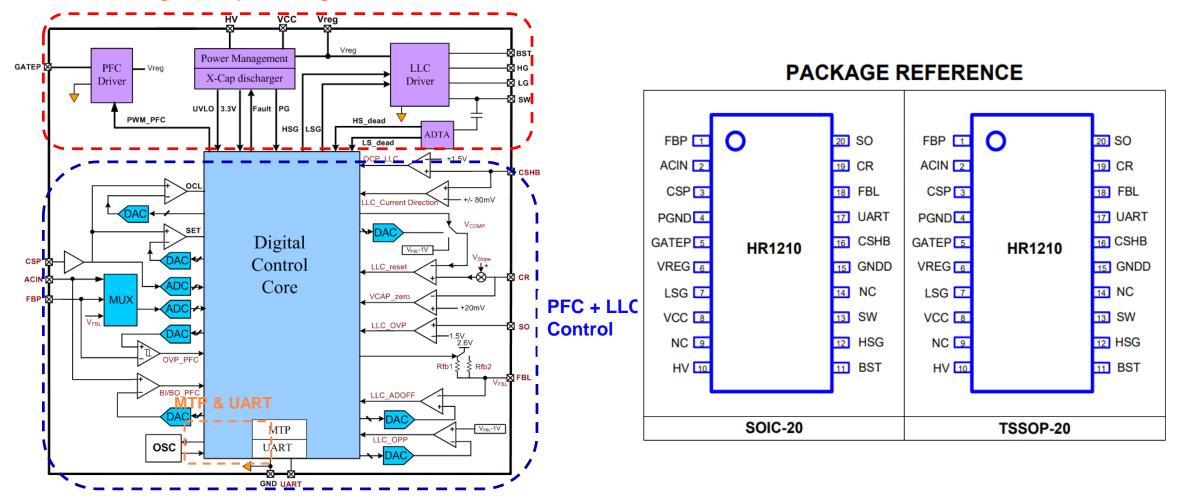

#### Driver, Power Manager, X-cap discharge, ADTA

# **HR1210 Key Features**

#### System:

- Pin<100mW@Pout=0mW</p>

- > High voltage current source for start up & Smart X-cap discharger

- > UART Interface & GUI for parameters program

#### **PFC:**

- > CCM/DCM operation of digital PFC (Max. Switching up to 250KHz)

- High PF due to cap current compensation (>0.95@ 20% load)

- > Programmable frequency Jitter to improve EMI.

- > Digital PI for control loop

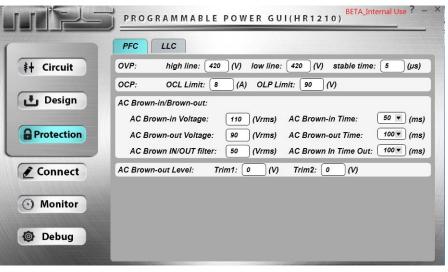

- > Programmable AC BI/BO, OVP, OCL, OLP

#### LLC:

- Current Mode / Voltage Mode Control

- Adaptive dead time adjustment (230ns~1us)

- Anti capacitive mode operation of LLC

- > Programmable BI/BO, SCP, OPP

- Skip mode & frequency controlled Burst mode for better light load efficiency & low audible noise

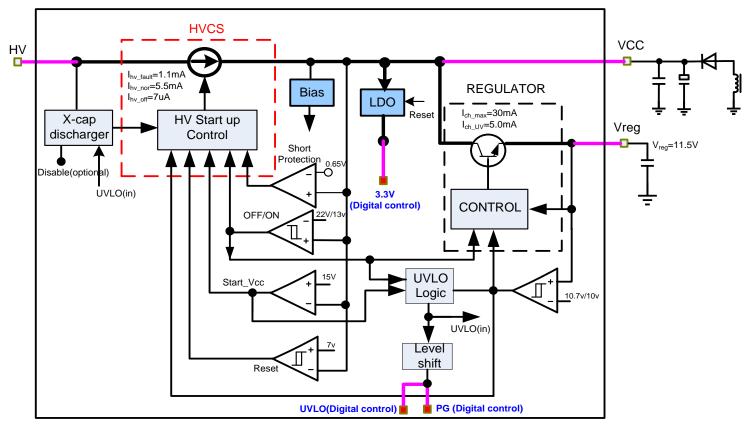

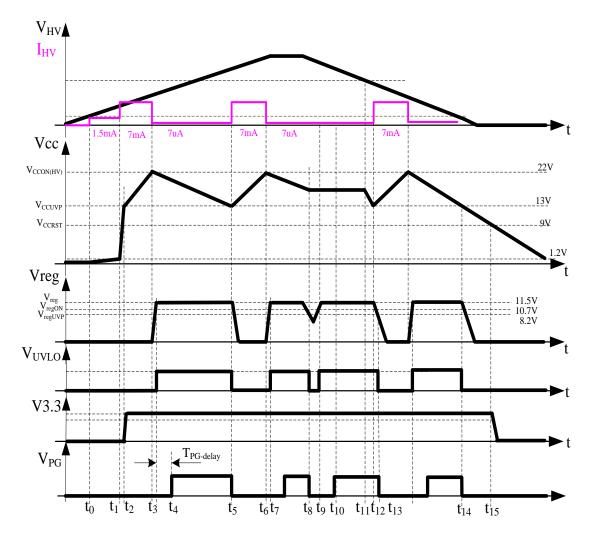

# HR1210-HVCS and X-cap discharge

- > A high voltage current source (HVCS) internal HV pin is used to power up VCC

- > An internal 3.3V LDO is used to power digital control

- > An internal 11V regulator is used to power the gate driver (Vreg)

- > UVLO and PG logic signal is generated for the digital control set-up

- > X-cap Discharge is detected on HV pin

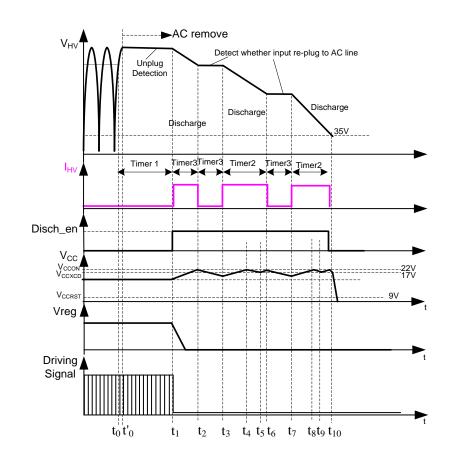

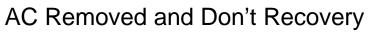

# HR1210-HVCS and X-cap discharge

#### Power Supply:

#### Normal Mode: V<sub>HV</sub> is sinusoid

t0: V<sub>HV-PK</sub> >35v, HVCS start charge Vcc.

t0~t1: 3.3v (digital control) power set-up

t3: V<sub>cc</sub> >22v, HVCS turn off, Vreg LDO (driver supply) works

t3: UVLO is high, digital control stand-by to operate

t4: PG (power good) is high, digital control starts soft-start

t4-t5: Capacitor value on Vcc determine this period.

t5-t8: Digital control stop work when Vcc<13v or Vreg<8.9v

# HR1210-HVCS and X-cap discharge

<u>X-Cap Discharger:</u> When  $V_{HV}$  is DC or Open. Vcc will regulate in 17v~22v

AC Remove but Recovery

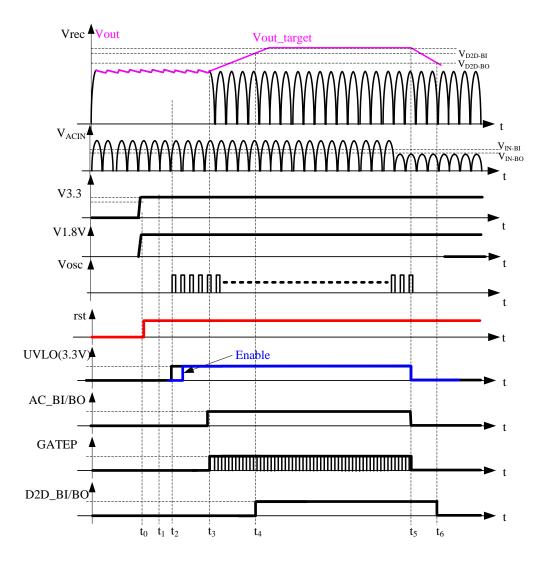

# HR1210-PFC+LLC digital control timing

t0: Internal 1.8V supply set-up when 3.3V is ready, rst signal set-up to reset digital.

t2: UVLO high, digital control start works, sense FBP, FBL, ACIN, CSP voltage

t2~t3:  $V_{in} > V_{in-BI}$ , with a timer, PFC start works

t3~t4: PFC Soft Start, LLC works when V<sub>put</sub>>V<sub>D2D\_BI</sub>

t4~t5: Normal operation

t5: V<sub>in</sub> <V<sub>in-BO</sub> with a timer, PFC stops switching

t6: V<sub>out</sub> <V<sub>D2D-BO</sub>, LLC stops switching.

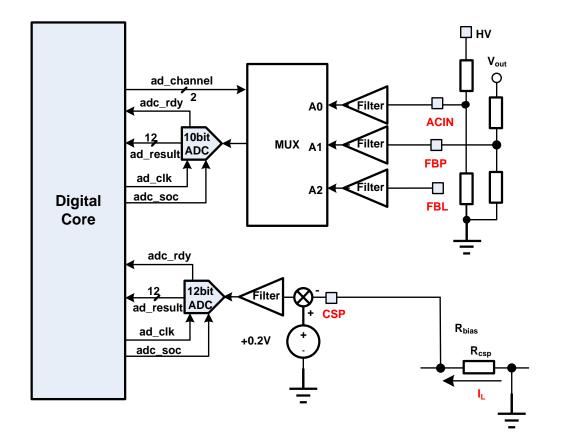

# HR1210-PFC+LLC digital control sampling

- The digital core need to sample FBP (PFC output), ACIN (PFC input) & CSP (PFC inductor current) for PFC control

- The digital core need to sample FBL (LLC Feedback) for LLC control

- The FBP, FBL & ACIN is sampled by a 10bit ADC through a controlled MUX

- > The CSP is sampled by a 12bit ADC

- The CSP is a negative voltage with internal biased by a 0.2V voltage source, so the sampled voltage of CSP is actually 0.2V-V<sub>CSP</sub>.

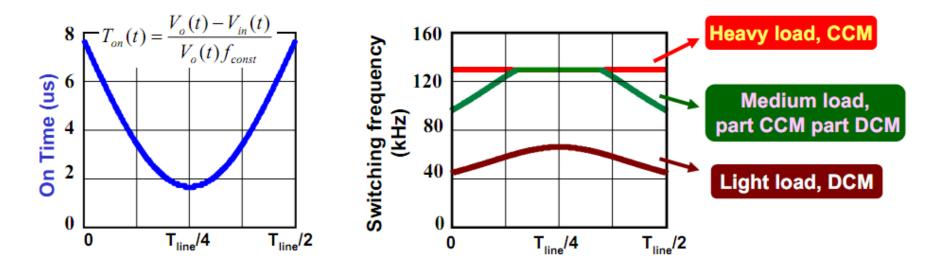

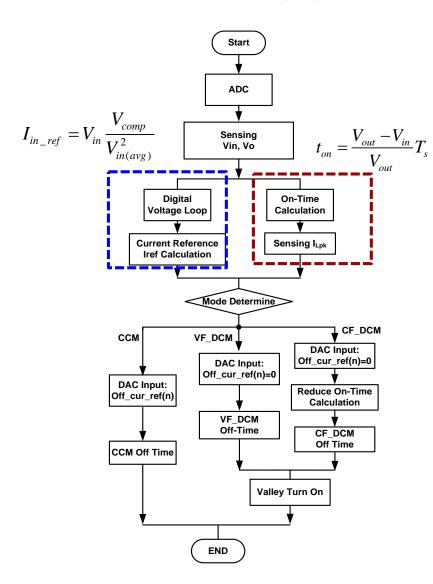

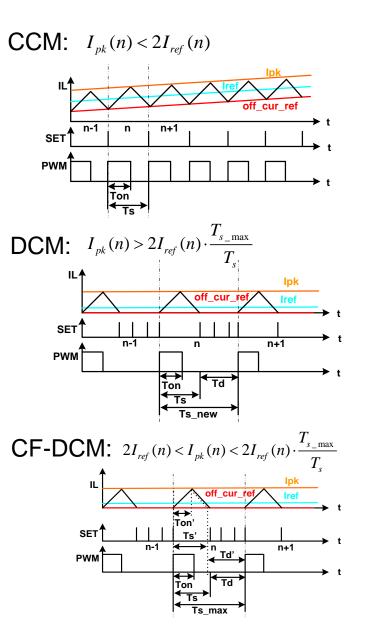

#### **Digital PFC: Quasi-fixed On Time Control**

By fix the Ton profile at different load conditions, switching frequency at light load can be reduced.

- On time is adaptively changed based on instantaneous input voltage.

- Light load efficiency can be improved.

#### Flowchart in 1 switching cycle:

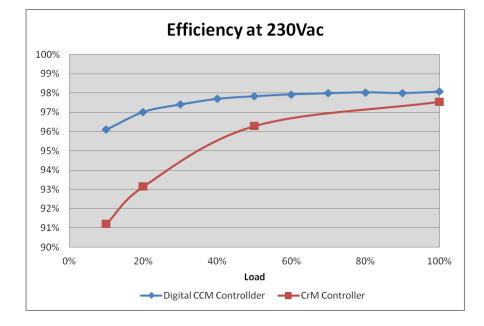

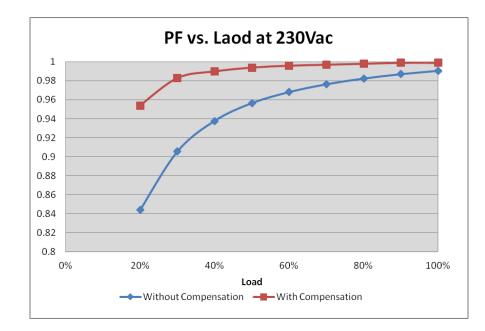

#### Key Performance:

- High light load Efficiency, >96% @ 10% load of 400w output

- High light load PF, >0.95 @ 20% load for 400w output.

#### PFC Protection:

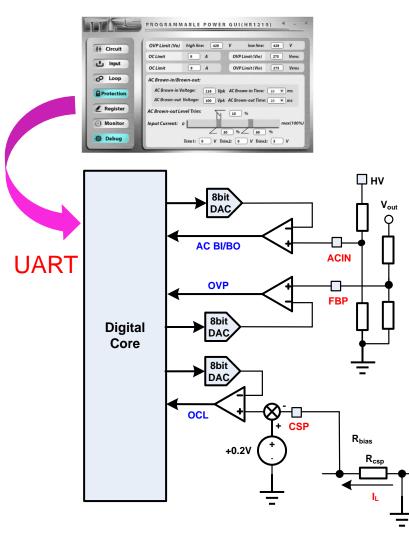

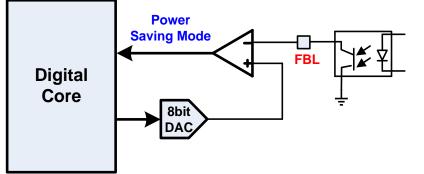

- The digital core control the threshold for AC BI/BO, OVP & OCL protection for PFC.

- A 8bit DAC is used for the output of the threshold of the protection

- By setting in GUI, the thresholds for these protection can be programmed through UART interface on IC.

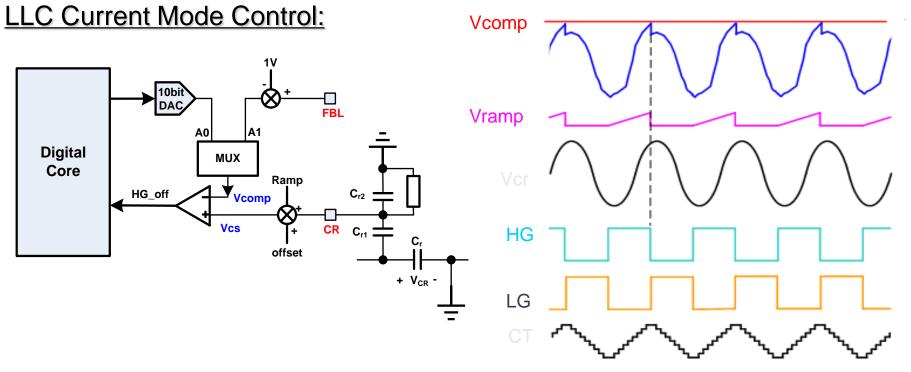

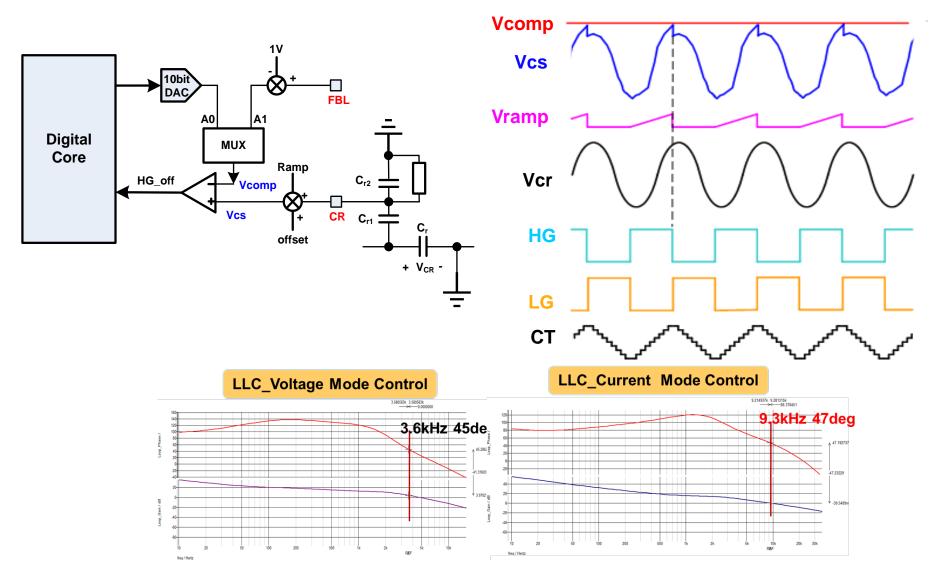

- The voltage on resonant cap (Cr) is compared with internal reference (Vcomp) to generate the HG-off signal

- > The LG on time is equal with HG on time by an internal

- The Internal reference (Vcomp) is derived from FBL pin voltage or digital core (10 bit DAC), depend by LLC operating state: When in steady state, Vcomp=VFBL-1V

When in Skip or burst mode, Vcomp=VDAC which determined by digital core

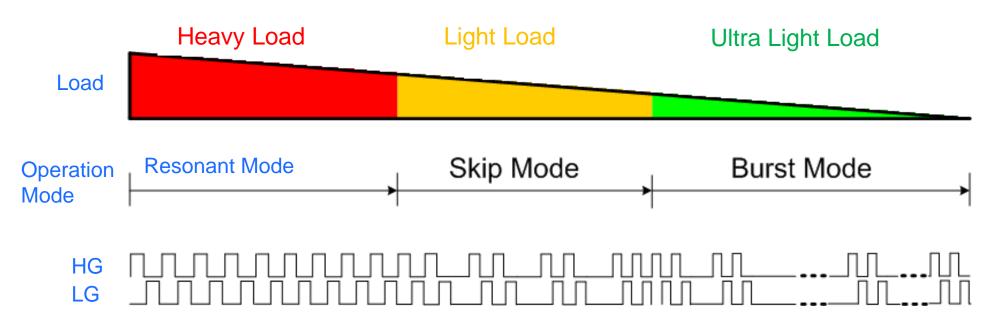

#### LLC Operating Mode:

>LLC changes operation mode according to the load.

➢It works in Resonant Mode (normal operation) at heavy load, switching to Skip Mode at lighter load and change to Burst Mode at ultra light load or no load.

>When run into Burst Mode, it works in PWM burst pattern to reduce audible noise.

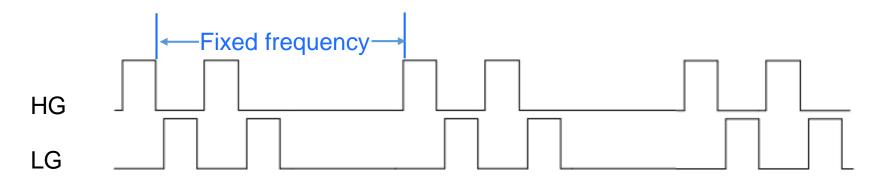

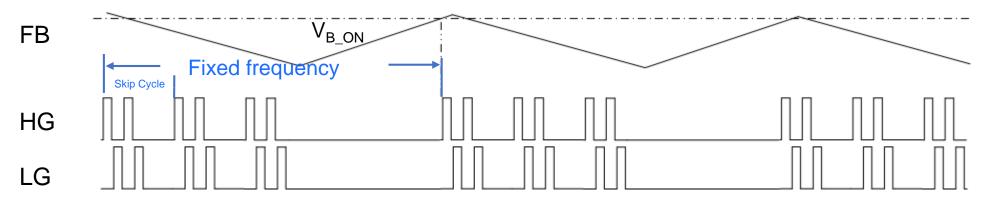

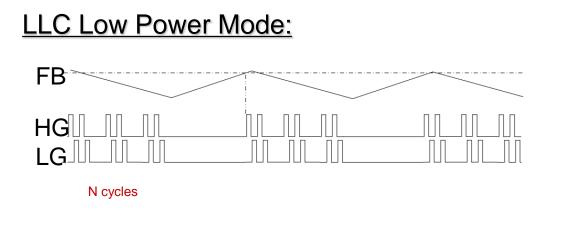

#### LLC Skip Mode:

- At light load, HG & LG stops switching for a certain period every N cycles (programmable)

- > The skip frequency is kept at fs (programmable)

#### LLC Burst Mode:

- At very light load condition, HG & LG switch in skip mode and stops switching for a long time which determined by VFBL touching the burst-on threshold (V<sub>B\_ON</sub>)

- The burst frequency can be select to keep at fs (programmable) for low audible noise

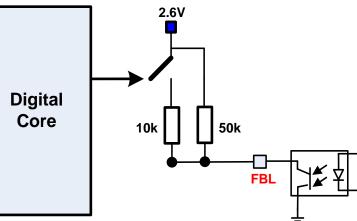

➢ When the LLC switching cycles N during each burst-on period is lower than a preset value (defined by GUI), the digital core will switch the FBL pull up resistor from ~8kOhm to 50kOhm to pull down the opto current

➢ When VFBL voltage (during burst-off) is lower than a preset value (defined by GUI), the IC will enter

➢ In power saving mode, the IC will only active some necessary internal circuits, which help to decrease the

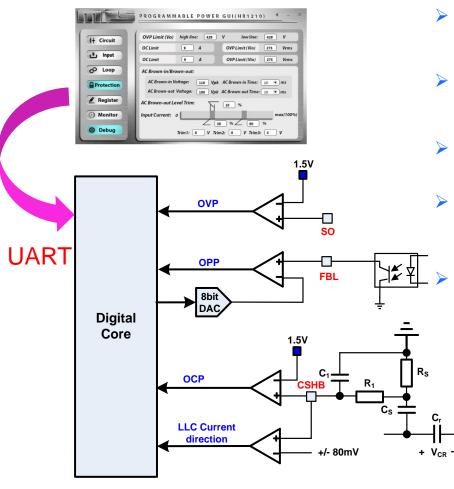

#### LLC Protection:

- The digital core control the threshold for OPP protection for LLC.

- The OVP protection is achieved by SO pin with fixed 1.5V threshold

- > The CSHB pin is used to sense the LLC current

- The OCP protection is achieved by compare current sense voltage on CSHB with 1.5V fixed threshold.

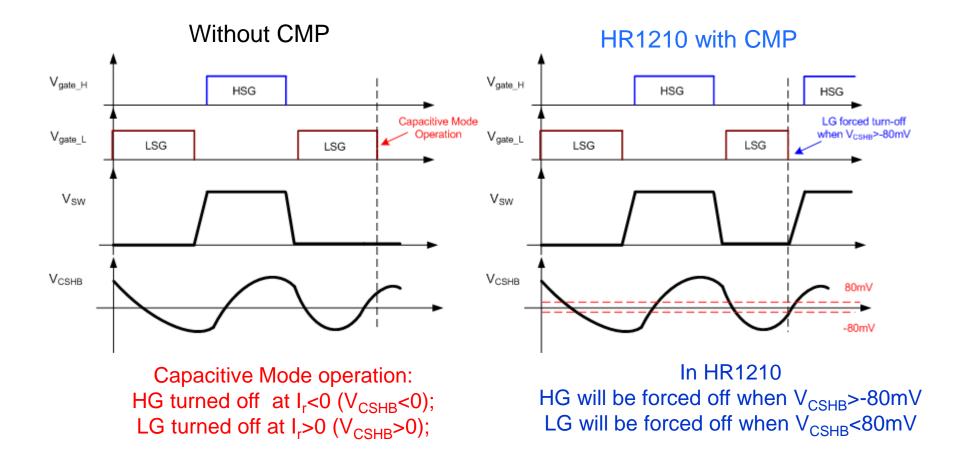

The digital core also sense the current direction of LLC by comparing the CSHB voltage with fixed +/- 80mV threshold (This used for CMP of LLC, see next page)

#### CMP (Capacitive Mode Protection):

**MPS**

# HR1210 key features

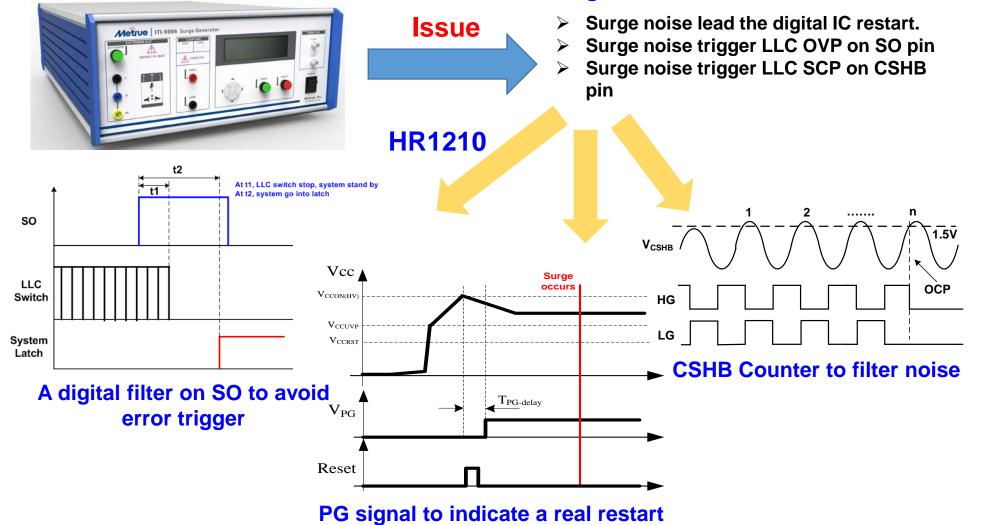

#### **Enhanced Surge Immunity**

# System shutdown & output drops when surge occur:

# HR1210 key features

#### **Current Mode Control LLC with better loop response**

# HR1210 User GUI for Parameters Configuration

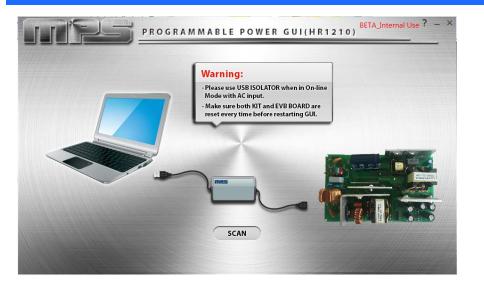

#### **Step1: Connection Kits**

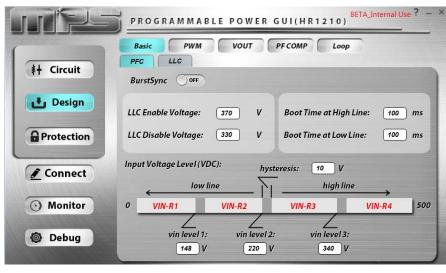

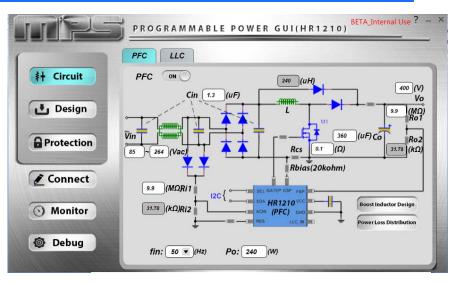

#### **Step2: Configuration Parameters**

Input PFC & LLC Design Parameters

Input PFC & LLC Protection Parameters

# **HR1210 User GUI for Parameters Configuration**

#### **Use GUI for Parameters Configuration :**

| + Circuit  | Command code | Command name                | Register value |         |

|------------|--------------|-----------------------------|----------------|---------|

| 1 encone   | 02H          | Manufactor and Project code | 0001           |         |

| 14         | 03H          | VBUS_CMD_H1                 | 031E           |         |

| • Design   | 04H          | VBUS_CMD_H2                 | 031E           |         |

|            | 05H          | VBUS_CMD_H3                 | 031E           |         |

| Protection | 06H          | VBUS_CMD_H4                 | 031E           | Program |

|            | 07H          | VBUS_CMD_L1                 | 031E           |         |

|            | 08H          | VBUS_CMD_L2                 | 031E           | Export  |

|            | 09H          | VBUS_CMD_L3                 | 031E           | Export  |

| Connect    | 0AH          | VBUS_CMD_L4                 | 031E           |         |

|            | 0BH          | AUTO_VBUS_VCOMP1            | 07AA           | Import  |

| Monitor    | 0CH          | AUTO_VBUS_VCOMP2            | 0311           |         |

|            | 0DH          | AUTO_VBUS_VCOMP3            | 013A           |         |

|            | 0EH          | AUTO_VBUS_VCOMPHYS          | 00C4           |         |

| > Debug    | OFH          | PFC_TS_MIN1                 | 03E8           |         |

Import & Export Register List

# **HR1210 User GUI for Parameters Configuration**

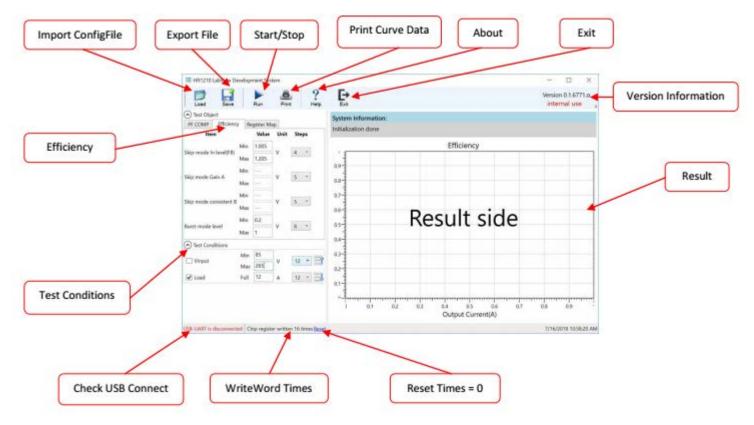

#### **Design Optimization with Labview:**

Use labview to get optimized parameters to improve the design

# HR1210 Design Optimization with LabView

# Appendix

#### HR1210 Demo Board (12V/33.3A):

#### **TOP VIEW**

#### **BOTTOM VIEW**

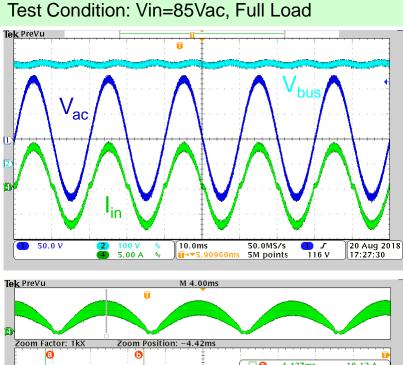

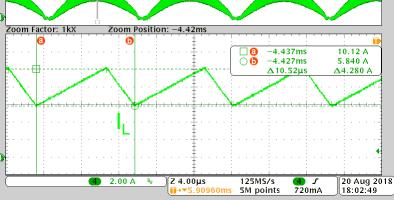

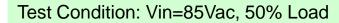

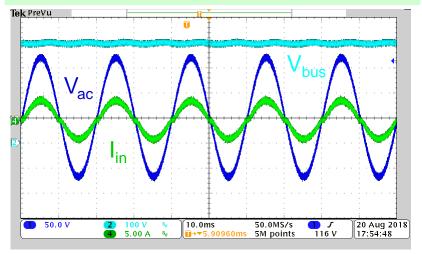

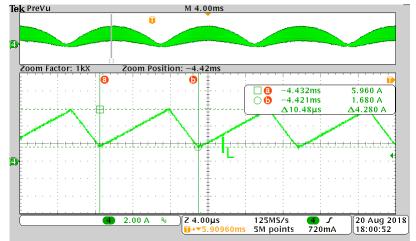

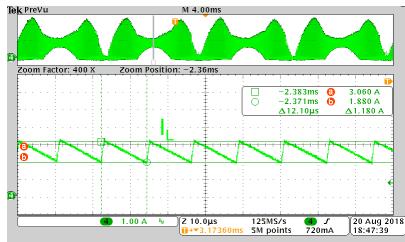

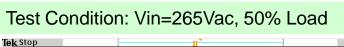

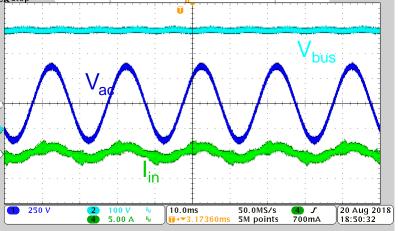

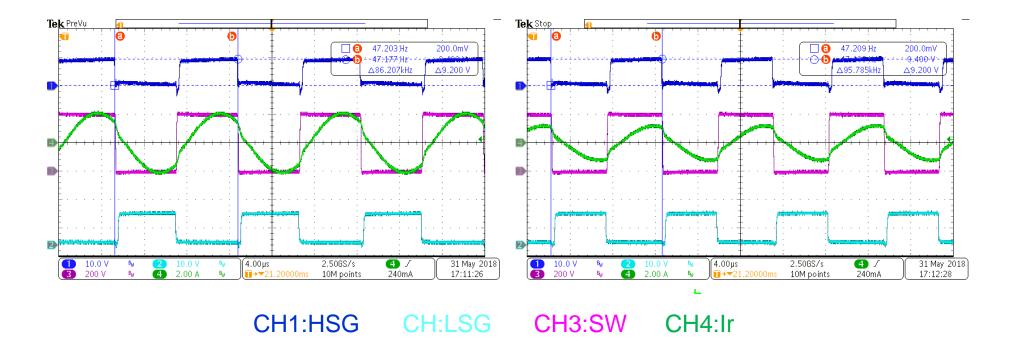

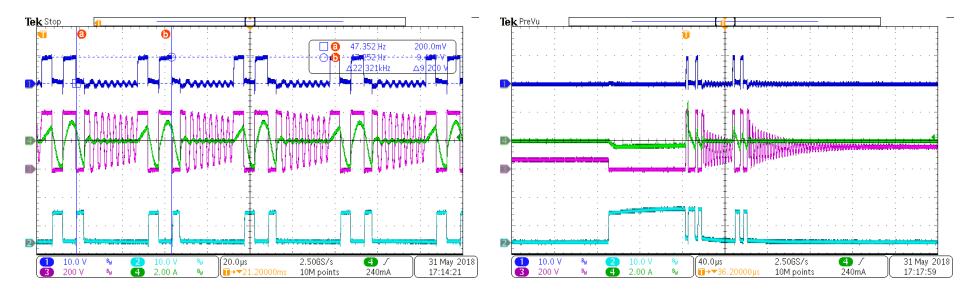

#### Steady State Waveform (PFC):

#### Steady State Waveform (PFC):

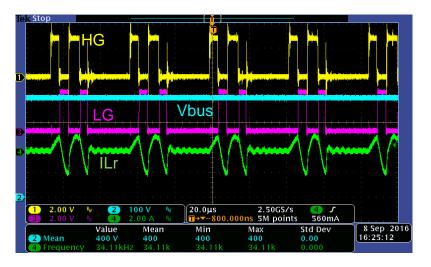

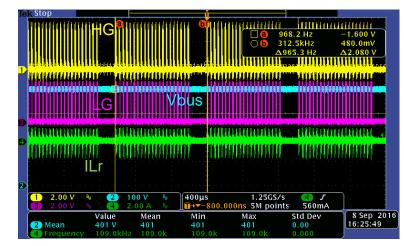

#### Steady State Waveform (LLC):

Test Condition: Vin=220Vrms, Io=20A

Test Condition: Vin=220Vrms, Io=10A

#### Steady State Waveform (LLC):

Test Condition: Vin=220Vrms, Io=5A

Test Condition: Vin=220Vrms, Io=0A

CH1:HSG CH2:LSG

CH3:SW CH4:Ir

#### No Load Power Consumption:

| Vin                 | 85Vac   | 115Vac  | 230Vac  | 265Vac  |

|---------------------|---------|---------|---------|---------|

| No load consumption | 93.79mW | 94.30mW | 97.18mW | 99.47mW |

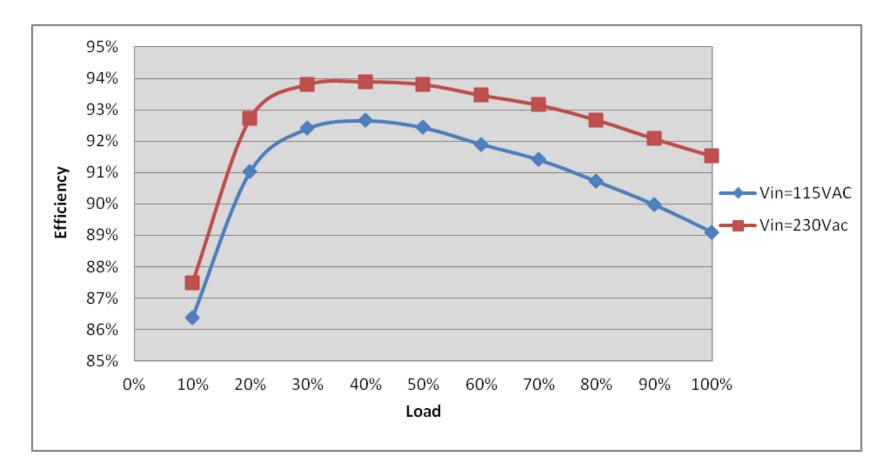

#### Total Efficiency:

#### Features

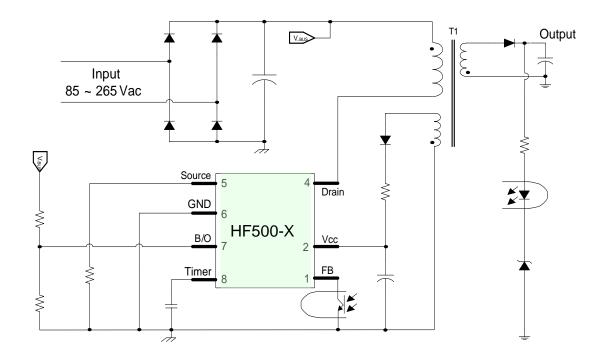

### Typical application

- 700V FET integrated

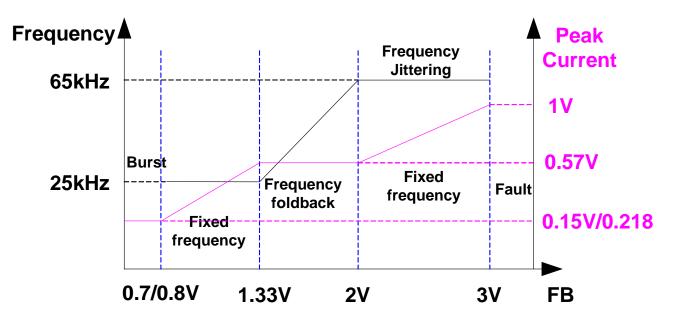

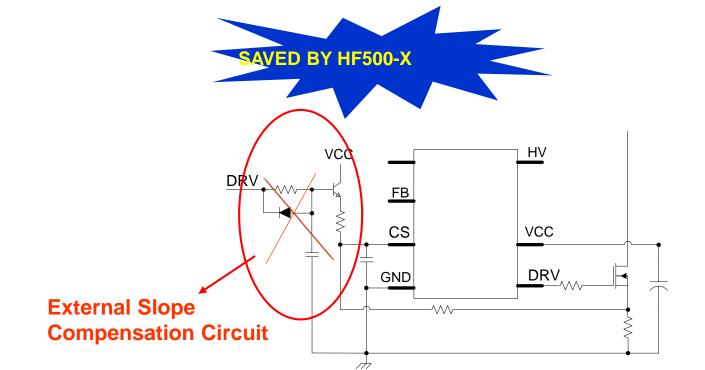

- Fixed-frequency current mode control operation with built-in slope compensation

- Frequency Foldback down to 25kHz at light load condition

- Burst Mode for low standby power consumption

- Frequency jittering for a reduced EMI signature

- Over power compensation

- Internal high voltage current source

- VCC UVLO

- Programmable input B/O and OVP

- Over Load Protection with programmable delay

- Latch-off protection on TIMER pin

- OVP, OTP, SCP

- Programmable soft start

### HF500-X Family

| Part No               | HF500-7  | HF500-15  | HF500-30  | HF500-40  |  |

|-----------------------|----------|-----------|-----------|-----------|--|

| Package               | SOIC8-7  | SOIC8-7   | DIP8-7    | DIP8-7    |  |

| Integrated Mosfet Ron | 12Ω/700V | 4.5Ω/700V | 1.4Ω/700V | 1.0Ω/700V |  |

| Power Rating Target   | 5-7W     | 7-15W     | 25-30W    | 35-40W    |  |

All parts released

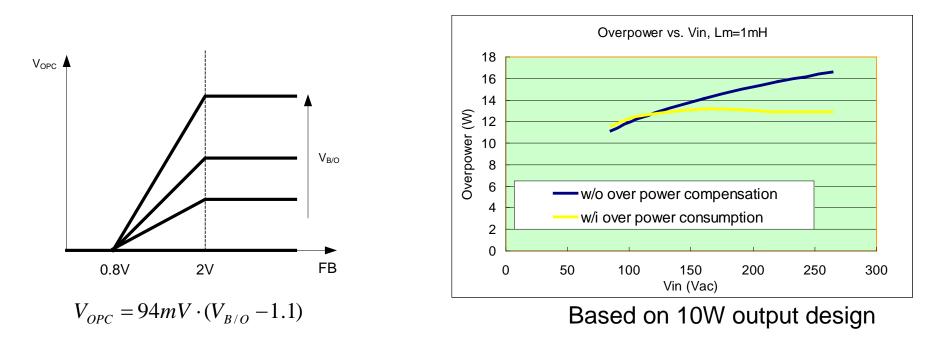

#### > Over Power Compensation

The over power point can be kept similar both in low line and high line.

### Frequency Foldback

Frequency foldback at light load condition for higher efficiency and low no load power consumption.

#### Internal Slope Compensation

Converter keeps stable when duty cycle is larger than 0.5 in CCM.

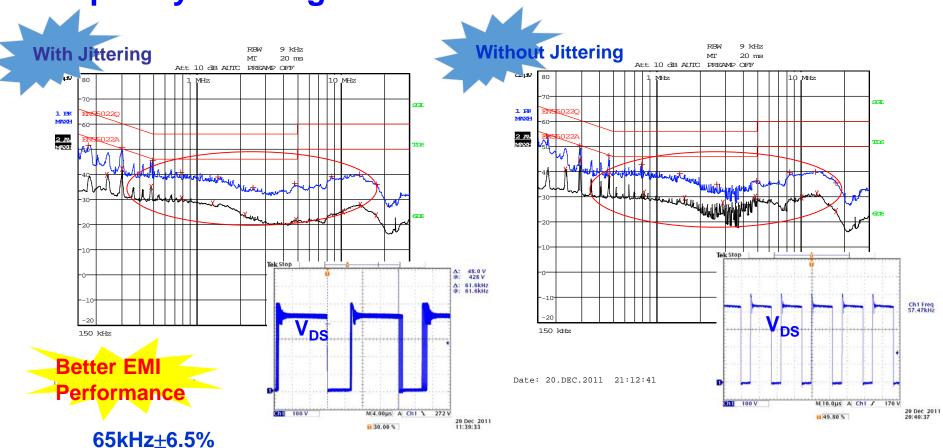

#### Frequency Jittering

Frequency jittering which leads to better EMI performance.

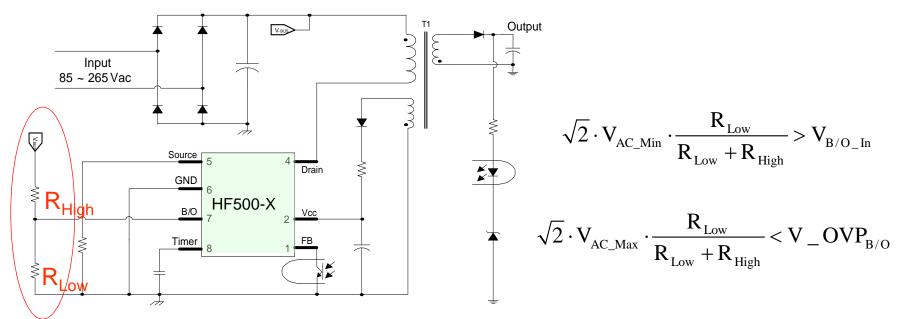

#### > Input Brown Out and OVP Function

By selecting the proper resistor divider, the input B/O and OVP can be realized by B/O pin.