# **MP6602 Configuration** By Pete Millett August 2022

# **MPS**

# TABLE OF CONTENTS

| Table of Contents                                                                                          | 2  |

|------------------------------------------------------------------------------------------------------------|----|

| Introduction                                                                                               | 3  |

| Step Mode Selection                                                                                        | 4  |

| Step Mode Register Configuration (MS2:MS0)                                                                 | 4  |

| Direct Step Configuration (TSTP)                                                                           | 4  |

| Current Setting and Automatic Hold                                                                         | 4  |

| Motor Winding Current Register Configuration (IS5:IS0 and IL5:IL0)                                         | 5  |

| Automatic Hold Current Register Configuration (AH2:AH0)                                                    | 5  |

| Off Time and Blanking Time Selection                                                                       | 6  |

| Off Time Register Configuration (OT2:OT0)                                                                  | 6  |

| Blanking Time Register Configuration (BT2:BT0)                                                             | 9  |

| Off Time and Blanking Time Set-Up Procedure                                                                | 10 |

| Stall Detection Configuration                                                                              | 10 |

| Back Electromotive Force (EMF) Voltage and Phase                                                           | 10 |

| Stall Detection Architecture                                                                               | 14 |

| Back EMF Register (BE7:BE0, Read-Only)                                                                     | 14 |

| Back EMF Gain Register Configuration (BEG2:BEG0)                                                           | 14 |

| Back EMF Averaging Register Configuration (BEMFSEL)                                                        | 15 |

| Back EMF Sample Point Register Configuration (BES1:BES0)                                                   | 15 |

| Stall Detection Threshold Register Configuration (STH7:STH0)                                               | 16 |

| Stall Detection Count Register Configuration (SDT3:STD0)                                                   | 17 |

| Fault Detection and Configuration                                                                          | 18 |

| Over-Current Protection (OCPAH, OCPAL, OCPBH, OCPBL, OCP)                                                  | 18 |

| $V_{\text{IN}}$ Under-Voltage Protection (UVP), VCC UVP, and $V_{\text{IN}}$ Over-Voltage Protection (OVP) | 18 |

| Over-Temperature Warning (OTW) and Over-Temperature Shutdown (OTS)                                         | 19 |

| Open-Load Detection (OLDIS, OLA, OLB)                                                                      | 19 |

| Stall Detection (STALL)                                                                                    | 19 |

### INTRODUCTION

The MP6602 is a powerful stepper motor driver with many advanced features, including the ability to detect a rotor stall.

For optimal use of these features, it is necessary to understand how they work, and how to configure the internal registers correctly.

The MP6602 registers can be configured via an SPI serial interface. During evaluation, a serial interface (e.g. the EVKT-USBI2C) and a Windows-based GUI can be used to optimize the MP6602's settings, either in the target hardware or with an evaluation board (e.g. the EV6602-V-01A). Since the registers are volatile and reset to their default values during start-up, a microcontroller is typically used to initialize the registers after start-up.

Refer to the MP6602 and EV6602-V-01A datasheets for more information.

## CONTROL REGISTER BITS (EN, STEP, AND DIR)

There are three bits in the CTRL register that can be used to control the motor: EN, STEP, and DIR.

The EN and DIR bits operate in the same manner as the ENBL and DIR pins. The CTRL register value is "exclusive-or'ed" with the pin value. For example, if the EN bit is set or if the ENBL pin is pulled high, then the part is enabled. If both the EN bit and the ENBL pin have the same value, then the part is disabled. Similarly, the part's rotation direction is set by the DIR bit and the DIR pin.

The motor advances one step at each rising edge of the STEP pin. It also advances each time a "1" is written to the STEP bit. Note that the bit does not have to be written again to "0". A step is taken each time a "1" is written, regardless of the current register value.

#### **STEP MODE SELECTION**

The step mode is the degree of microstepping that drives the motor. The MP6602 supports step modes between full step and 1/32 step.

#### Step Mode Register Configuration (MS2:MS0)

Choose the step mode based on the application. Motion is often smoother and quieter while using smaller microsteps (e.g. 1/32 steps); however, the incremental torque generated per microstep is also lower while, and the motion may not be as continuous as desired for the application. For high-torque and high-speed applications, it is recommended to choose a lower step modes.

The step mode is selected by the MS2:MS0 bits in the CTRL register (see Table 1).

| MS2:MS0 | Step Mode       |

|---------|-----------------|

| 000     | Full step (70%) |

| 001     | Half step       |

| 010     | Quarter step    |

| 011 (1) | Eighth step     |

| 100     | 1/16 step       |

| 101     | 1/32 step       |

| Table | 1. | Sten | Mode | Selection |

|-------|----|------|------|-----------|

| Iable |    | Siep | woue | Selection |

#### Note:

1) Reset value.

#### **Direct Step Configuration (TSTP)**

The motor can be sent to a specific step by writing to the TSTP register. Refer to the MP6602 datasheet for more details.

Only values appropriate to the configured step mode can be written to the TSTP register. For example, in half-step mode, the lower bits of the TSTP register are ignored, and only the half-step mode settings are recognized.

#### **CURRENT SETTING AND AUTOMATIC HOLD**

The motor current is determined by the amount of torque required in an application, as well as the stepper motor ratings. The maximum current is configured, and the winding currents are modulated based on the selected step mode. Full-step mode always uses 70% of the set peak current.

A higher current results in more torque being generated. It also consumes more power, and causes the motor temperature to increase. Ensure that the maximum current setting does not exceed the motor ratings. Exceeding the motor current ratings may cause thermal damage or demagnetization of the rotor. However, the current should be set high enough to prevent the motor from stalling (i.e. not completing a step).

#### Motor Winding Current Register Configuration (IS5:IS0 and IL5:IL0)

The peak regulation current ( $I_{100\%}$ ) is set by the IS5:IS0 bits in the ISET register. Table 2 shows the ISET register bit settings for different peak regulation currents.

| IS5:IS0, IL5:IL0    | Peak Regulation<br>Current (I100%) |  |  |  |  |

|---------------------|------------------------------------|--|--|--|--|

| 0x00                | 125mA                              |  |  |  |  |

| 0x01                | 250mA                              |  |  |  |  |

| 0x02                | 375mA                              |  |  |  |  |

| 0x03                | 500mA                              |  |  |  |  |

| 0x04                | 625mA                              |  |  |  |  |

| 0x05                | 750mA                              |  |  |  |  |

| 0x06                | 825mA                              |  |  |  |  |

| 0x07                | 1A                                 |  |  |  |  |

| 0x08                | 1.13A                              |  |  |  |  |

| 0x09 <sup>(2)</sup> | 1.25A                              |  |  |  |  |

| 0x0A                | 1.38A                              |  |  |  |  |

| 0x0B                | 1.5A                               |  |  |  |  |

| 0x0C                | 1.63A                              |  |  |  |  |

| 0x0D                | 1.75A                              |  |  |  |  |

| 0x0E                | 1.88A                              |  |  |  |  |

| 0x0F                | 2A                                 |  |  |  |  |

| 0x10                | 2.13A                              |  |  |  |  |

| 0x11                | 2.25A                              |  |  |  |  |

| 0x12                | 2.38A                              |  |  |  |  |

| 0x13                | 2.5A                               |  |  |  |  |

| 0x14                | 2.63A                              |  |  |  |  |

| 0x15                | 2.75A                              |  |  |  |  |

| 0x16                | 2.88A                              |  |  |  |  |

| 0x17                | 3A                                 |  |  |  |  |

| 0x18                | 3.13A                              |  |  |  |  |

| 0x19                | 3.25A                              |  |  |  |  |

| 0x1A                | 3.38A                              |  |  |  |  |

| 0x1B                | 3.5A                               |  |  |  |  |

| 0x1C                | 3.63A                              |  |  |  |  |

| 0x1D                | 3.75A                              |  |  |  |  |

| 0x1E                | 3.88A                              |  |  |  |  |

| 0x1F                | 4A                                 |  |  |  |  |

|                     |                                    |  |  |  |  |

#### Table 2: ISET Register Bit Settings for Different Peak Regulation Currents

Note:

2) Reset value.

The IL5:IL0 bits set the current once the automatic hold feature is enabled.

#### Automatic Hold Current Register Configuration (AH2:AH0)

To save power, the MP6602 has an automatic hold feature that reduces the winding current while the motor is stationary. If step activity has stopped for a set time period (configured via AH2:AH0), then automatic hold reduces the current to the level set by the IL5:IL0 bits in the ISET register.

Choose the automatic current based on the application's required holding torque. For example, if only

50% of the peak torque is required while the motor is not operating, then the hold current should be set to 50% of the peak current.

There is a configurable delay time between when the pulses on the STEP input stop and when the automatic hold function is active. This delay time should be long enough so that the automatic hold function is not active during normal motor operation.

The automatic hold function is controlled by the AH2:AH0 bits in the CTRL register. This register sets the configurable automatic hold time. If AH2:AH0 is set to 0, then the automatic hold function is disabled. Table 3 shows the CTRL register bit settings for different automatic hold times.

| AH2:AH0             | Automatic Hold<br>Delay Time | Minimum Steps<br>per Second |  |  |  |

|---------------------|------------------------------|-----------------------------|--|--|--|

| 0x00 <sup>(3)</sup> | Disabled                     | -                           |  |  |  |

| 0x01                | 15.6ms                       | 64                          |  |  |  |

| 0x02                | 31.3ms                       | 32<br>16                    |  |  |  |

| 0x03                | 62.5ms                       |                             |  |  |  |

| 0x04                | 125ms                        | 8                           |  |  |  |

| 0x05                | 250ms                        | 4                           |  |  |  |

| 0x06                | 500ms                        | 2                           |  |  |  |

| 0x07                | 1000ms                       | 1                           |  |  |  |

#### Table 3: CTRL Register Bit Settings for Different Automatic Hold Times

#### Note:

3) Reset value.

#### OFF TIME AND BLANKING TIME SELECTION

Current regulation in a winding works by turning the outputs on and off. This modulates the pulse width to regulate the current. Since the winding is inductive, applying a voltage across it makes the current increase at a rate determined by the motor winding's inductance and the applied voltage.

Once the current has reached the regulation level, the current is turned off for a fixed amount of time. Then the cycle repeats.

#### Off Time Register Configuration (OT2:OT0)

The constant off time ( $t_{OFF}$ ) is set by the OT2:OT0 bits in the CTRL register. Table 4 shows CTRL register settings for different off times.

| OT2:OT0 | toff (µs) |

|---------|-----------|

| 000     | 20        |

| 001     | 25        |

| 010     | 30        |

| 011     | 35        |

| 100 (4) | 40        |

| 101     | 45        |

| 110     | 50        |

| 111     | 55        |

Note:

4) Reset value.

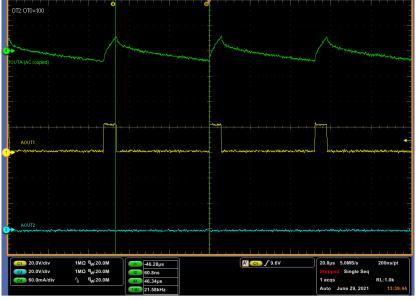

Figure 1 and Figure 2 on page 7, as well as Figure 3 and Figure 4 on page 8 show what occurs if  $t_{OFF}$  is changed. Figure 1 on page 7 shows a waveform where the OT2:OT0 bits are set to 000 ( $t_{OFF}$  is 20µs).

Figure 1: toFF = 20µs

The time between pulses is short (about  $20\mu$ s). The switching frequency ( $f_{SW}$ ) at this current level is about 45kHz, and all of switching cycles are in slow decay. This means that the winding current drops slowly while the winding is shorted during  $t_{OFF}$ .

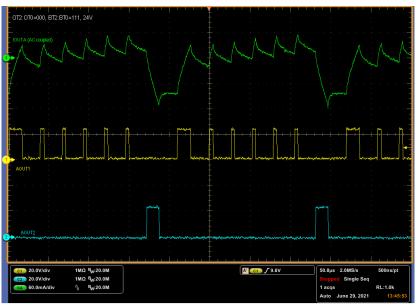

Figure 2 shows a waveform where the OT2:OT0 bits are set to 100 ( $t_{OFF}$  is 40µs).

Figure 2: toff = 40µs

$t_{OFF}$  is extended, and the  $f_{SW}$  is about 20kHz.

$t_{OFF}$  sets the maximum PWM frequency. A shorter  $t_{OFF}$  results in higher  $f_{SW}$ . Note that  $f_{SW}$  is not constant. Higher currents require a longer on time ( $t_{ON}$ ); therefore,  $f_{SW}$  varies with current, and consists of both  $t_{ON}$  and  $t_{OFF}$ .

The optimal  $t_{OFF}$  is determined by the motor inductance and supply voltage. Low-inductance motors or a high supply voltage requires a shorter  $t_{OFF}$ . If  $t_{OFF}$  is too long, then the current may decrease too rapidly, and  $t_{ON}$  is extended. A longer  $t_{ON}$  increases the device's ripple current.

If  $t_{OFF}$  is too short, then the controller cannot decrease the current fast enough by turning it off. This allows the current to continue to build in each cycle. In this scenario, the MP6602 employs fast decay, which reduces the current rapidly. During fast decay, the winding's current is reversed in order to reduce the current. Figure 3 shows fast decay.

Figure 3: Fast Decay

Figure 4 shows six slow decay cycles (where the current is increasing), followed by one fast decay cycle that reduces the current.

#### Figure 4: Mixed Decay

$t_{OFF}$  is set to the its minimum setting, and the blanking time ( $t_{BLANK}$ ) is set to its maximum setting. This results in the longest minimum  $t_{ON}$ , and shortest  $t_{OFF}$ .

At lower supply voltages with the same register settings, the current does not increase as quickly (see Figure 3).

#### Blanking Time Register Configuration (BT2:BT0)

Note that the decay behavior is also affected by  $t_{BLANK}$ .  $t_{BLANK}$  disables the current trip level for a short period of time after an output is turned on. This prevents a false trip caused by parasitic capacitance (e.g. intrawinding capacitance), which means  $t_{BLANK}$  also sets the minimum  $t_{ON}$ . If the current rises quickly due to a high voltage or low inductance, then the current exceeds the set trip level, and the output does not turn off until  $t_{BLANK}$  has elapsed.

It is recommended to set  $t_{OFF}$  and  $t_{BLANK}$  to minimize this behavior, as it can result in audible noise while the motor is stationary.

$t_{BLANK}$  (which also sets the minimum  $t_{ON}$ ) can be configured via the BT2:BT0 bits in the CTRL2 register. Table 5 shows the CTRL2 register bit settings for different blanking times.

| <b>t</b> BLANK |

|----------------|

| 250ns          |

| 500ns          |

| 1µs            |

| 1.5µs          |

| 2µs            |

| 2.5µs          |

| 3µs            |

| 3.5µs          |

|                |

#### Table 5: CTRL2 Register Bit Settings for Different Blanking Times

Note:

5) Reset value.

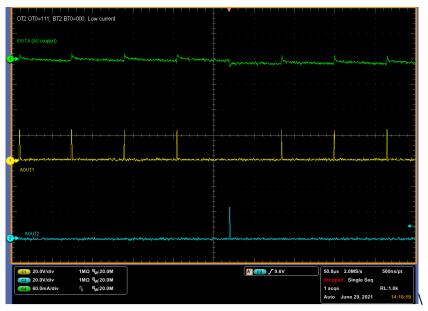

Even while operating at optimal settings, fast decay cycles are necessary while the MP6602 regulates very low currents (especially at the microsteps near 0A). This is also the case at the maximum  $t_{OFF}$  and at the minimum  $t_{BLANK}$ . Figure 5 shows the MP6602 regulating a very small current with very short on times, and the occasional fast decay cycle to regulate the current.

Figure 5: Low Current Regulation

#### Off Time and Blanking Time Set-Up Procedure

The MP6602's default settings are suitable for many applications; however, some applications may require other device settings to improve operation (especially if there is increased audible noise while the motor is not moving).

Some motor and voltage combinations may not allow for the exact optimization listed below, and may require compromise on some of the settings. The purpose of optimizing the settings is to achieve smooth current regulation while the motor is moving, and low noise while the motor is not moving.

Follow the steps below to optimize t<sub>OFF</sub> and t<sub>BLANK</sub>:

- 1. Connect the target motor to the MP6602, as well as a communication interface (EVKT-USBI2C) and GUI to configure the registers via the SPI interface. Do not apply pulses to the STEP input pin.

- 2. Connect an oscilloscope to the AOUT1 and AOUT2 pins to monitor bridge A's output terminals.

- 3. Connect a current probe to winding A to monitor the current flowing through the winding.

- 4. Apply the VCC voltage ( $V_{CC}$ ) and input voltage ( $V_{IN}$ ) to the MP6602.

- 5. Configure the ISET register, bits[5:0] to set the desired maximum winding current. (This can be set to the motor's maximum rated winding current.)

- 6. Set maximum  $t_{OFF}$  (OT2:OT0 = 111) and maximum  $t_{BLANK}$  (BT2:BT0 = 111).

- 7. Set the step mode to 1/32 (MS2:MS0 = 101).

- 8. Set the 100% current in the A output by writing "0" to the TSTP register. If using the MPS GUI, press the "STEP" button repeatedly until the STP value is 0.

- 9. Turn the motor on by pulling the ENBL pin high or writing the EN bit to 1.

- 10. Measure  $f_{SW}$  on OUT1 and OUT2. If  $f_{SW}$  is below 20kHz, set OT2:OT0 to shorten  $t_{OFF}$  until  $f_{SW}$  is  $\geq$ 20kHz. This reduces audible noise.

- 11. If there are multiple fast decay cycles, set BT2:BT0 to shorten t<sub>BLANK</sub> until the fast decay cycles disappear.

- 12. If the fast decay cycles persist (even at the minimum t<sub>BLANK</sub>), set OT2:OT0 to extend t<sub>OFF</sub>. Extending t<sub>OFF</sub> can drop f<sub>SW</sub> below 20kHz, which may cause audible noise.

- 13. Set the 38% current by writing "0x18h" to the TSTP register. If using the MPS GUI, press the "STEP" button repeatedly until the STP value is 0x18h.

- 14. Observe the switching. If there are fast decay cycles present, shorten t<sub>BLANK</sub> further to try and remove these cycle. Removing the fast decay cycles entirely may not be possible.

#### STALL DETECTION CONFIGURATION

Stall detection in the MP6602 is based on the motor's back electromotive force (EMF) measurement. If a stepper motor is rotating, then there is a back EMF generated that is proportional to the motor speed. The MP6602 measures this voltage directly at every zero-current step. In full-step mode there is not a zero current state; therefore, stall detection does not work in full-step mode.

Since stall detection is based on the back EMF measurement, the motor should be moving fast enough to have a measurable back EMF. Due to this, stall detection may not work well at very slow speeds (e.g. at a few steps per second), and it is typically difficult to determine whether a single step was executed.

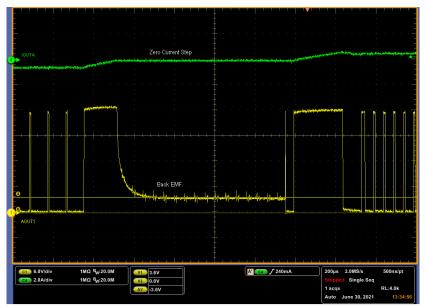

#### Back Electromotive Force (EMF) Voltage and Phase

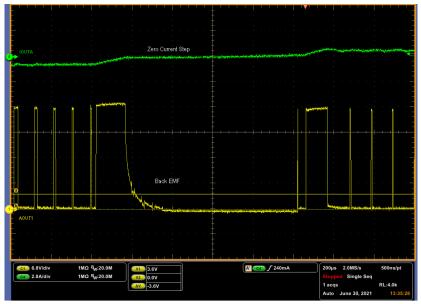

The back EMF can be observed with an oscilloscope. In continuous rotation (while the current in a winding drops to 0A), one side of the winding is in a high impedance (Hi-Z) state. The voltage drops and levels off at a point that represents the back EMF. The MP6602 samples this voltage and converts it to a digital

value. Figure 6 shows a waveform for a motor that is rotating freely, where the back EMF is about 3.6V.

Figure 6: Back EMF while Rotating

If the motor stalls (e.g. the rotor is locked, so the motor cannot move), the back EMF drops to 0V. Figure 7 shows a stalled motor.

Figure 7: Stalled Motor

If the rotor is completely stationary, then detecting a stall is simple; however, in real-world applications, the motor is often not completely stationary. For example, if the motor is run against a mechanical stop, then it typically bounces off the stop and vibrates. Even though the motion is not continuous, the bouncing causes a non-zero back EMF. Further processing is required to determine when a stall has occurred.

In addition to detecting a stall, the phase of the back EMF can be measured to estimate the torque applied to the motor, and an impending stall. The shape of the back EMF measurement vs. the applied torque varies substantially, and is determined by the motor and operating conditions. The phase can be measured indirectly by capturing the back EMF at a particular sample point. This results in different amplitude measurements as the phase of the back EMF shifts.

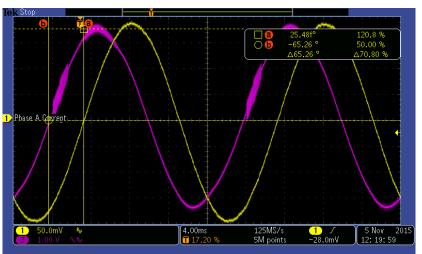

Figure 8 shows the current and voltage driven with an analog current source at very light loads on the motor.

Figure 8: Voltage and Current at No Load

The current lags the voltage by 65°. Notice the voltage amplitude (the magenta line) at the point where the current crosses 0A.

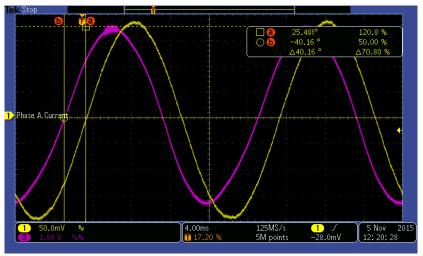

Figure 9 shows the motor voltage and current at heavy loads. The amplitude of the overall back EMF does not change much at heavy loads; however, the phase shifts (about 40° in Figure 9). The voltage amplitude at 0A is significantly lower.

Figure 9: Voltage and Current at Heavy Loads

This information can be used to estimate the measurement of the torque applied to the motor.

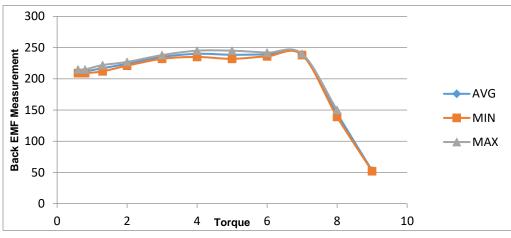

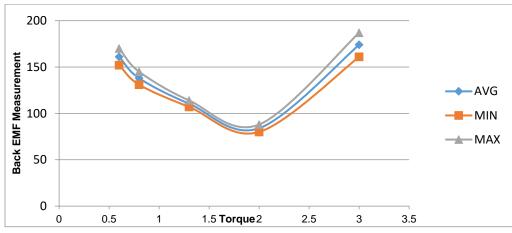

Figure 10 on page 13 shows the measured back EMF (at a particular sample point) and the torque applied to a stepper motor that is rotating continuously. As the torque approaches the stall, the back EMF drops. This is can help detect an impending stall before it occurs.

Figure 10: Back EMF vs. Torque (Sample Point 1)

Moving the sample point changes the shape of this curve. To make an reliable measurement of the torque, the sample point should be adjusted so that it provides an indication of torque over the desired range. This should be done experimentally, and is be different for every application.

Figure 11 shows different sample conditions. This set-up can measure the torque at low values, but cannot detect stalls.

Figure 11: Back EMF vs. Torque (Sample Point 2)

#### **Stall Detection Architecture**

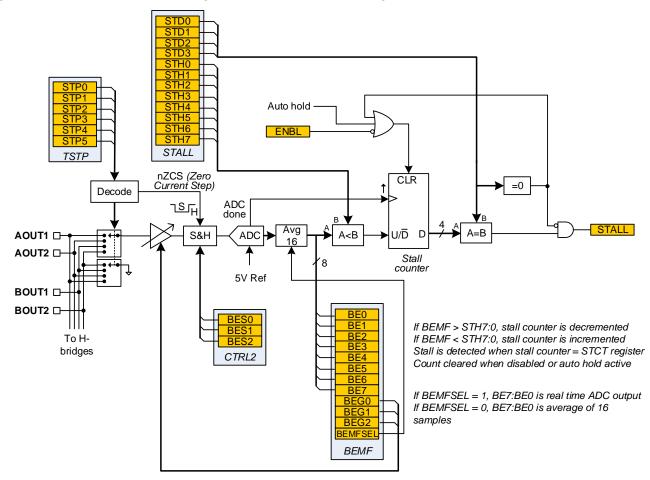

Figure 12 shows the MP6602's high-level architecture and registers of the stall detection circuit.

#### Figure 12: Stall Detection Circuit

Once the logic detects a stall, the STALL bit is set. This is treated as a fault. See the Fault Detection and Configuration section on page 18 for more details.

#### Back EMF Register (BE7:BE0, Read-Only)

The back EMF measurement (the A/D converter output) can be read via the BE7:BE0 register bits. The back EMF is sampled, held, and applied to an A/D converter. The A/D output is optionally averaged 16 times, and is available to read through the SPI interface via the read-only BE7:BE0 bits in the BEMF register.

The control registers also affect the operation of the A/D converter.

#### Back EMF Gain Register Configuration (BEG2:BEG0)

There is a configurable gain (or loss) between the OUTx pins and the A/D converter. The A/D converter has a full scale input (5V). The full scale back EMF is between 250mV and 50V.

The BEG bits are set so that the A/D converter can accurately measure the back EMF at the point where stall detection is desired. This back EMF level is determined by the motor construction and speed, and is less than the supply voltage.

| BEG2:BEG0           | Back EMF<br>Gain | Full-Scale<br>Back EMF |  |  |

|---------------------|------------------|------------------------|--|--|

| 0x00                | 0.1              | 50V                    |  |  |

| 0x01                | 0.2              | 25V                    |  |  |

| 0x02                | 0.5              | 10V                    |  |  |

| 0x03 <sup>(6)</sup> | 1                | 5V                     |  |  |

| 0x04                | 2                | 2.5V                   |  |  |

| 0x05                | 5                | 1V                     |  |  |

| 0x06                | 10               | 500mV                  |  |  |

| 0x07                | 20               | 250mV                  |  |  |

#### Table 6: BEMF Register Bit Settings for Different Back EMF Gain

#### Note:

6) Reset value.

The back EMF gain is set while the motor is operating under its typical operating conditions. Set the gain so that the back EMF read through the BE7:BE0 bits does not exceed the maximum value (0xFFh). In some cases (especially while the motor speed varies across a large range), the back EMF gain should be set to a higher level.

#### **Back EMF Averaging Register Configuration (BEMFSEL)**

The BEMFSEL bit in the BEMF register determines whether the A/D converter should update the realtime data at each zero-current step or at the previous 16 zero-current steps' average measurement. The default setting (average of 16 conversions) is suitable for most applications. If trying to detect stalls at very low speeds, the real-time setting may provide better results.

#### Back EMF Sample Point Register Configuration (BES1:BES0)

In most cases, a stall can be detected at very low motor speeds. Figure 13 shows the resulting back EMF of a 1 PPS step rate.

#### Figure 13: Single-Step Back EMF

There is some back EMF immediately after the step, which then decays. Some motor movement (and related back EMF) occur after the step due to mechanical resonances.

If the rotor is locked firmly, then the back EMF goes to 0V (see Figure 14 on page 16).

| 2 | - 101 |         |   |            |   |   |     | Zero Currei                                                          | nt Step    | +<br>+<br>+                               |                |        |            |                                                                 |                                  |

|---|-------|---------|---|------------|---|---|-----|----------------------------------------------------------------------|------------|-------------------------------------------|----------------|--------|------------|-----------------------------------------------------------------|----------------------------------|

|   |       |         |   |            |   | - |     |                                                                      |            |                                           |                |        |            |                                                                 | 4                                |

|   |       |         |   |            |   |   |     |                                                                      |            |                                           |                |        |            |                                                                 |                                  |

|   |       | ĺ       | 1 |            |   |   |     |                                                                      |            |                                           |                |        |            |                                                                 |                                  |

|   |       |         | + |            | - |   |     |                                                                      |            |                                           |                |        |            |                                                                 |                                  |

|   |       |         |   |            |   |   |     |                                                                      |            |                                           |                |        |            |                                                                 |                                  |

|   | 8     |         |   |            |   |   |     | Back EM                                                              | MF         |                                           |                |        |            |                                                                 |                                  |

| G | Dun   | ļ,      |   |            |   |   | Îψ. | unanonani                                                            | anindinana | İndundundundundundundundundundundundundun | uitinuu        | manna  | <u>unu</u> |                                                                 | <u>ainataina</u>                 |

|   | A0    |         |   |            |   |   |     |                                                                      |            |                                           |                |        |            |                                                                 |                                  |

|   |       |         |   |            |   |   |     |                                                                      |            |                                           |                |        |            |                                                                 |                                  |

|   |       | ) 6.0V/ |   | 1ΜΩ<br>1ΜΩ |   |   |     | V1         3.6V           V2         0.0V           ΔV         -3.6V |            |                                           | <b>∛ @ ? )</b> | -320mA | S          | .0ms 2.0MS/s<br>topped Single Seq<br>acqs<br>.uto June 30, 2021 | 500ns/pt<br>RL:20.0k<br>13:54:46 |

Figure 14: Stalled Back EMF

The key to detecting the type of stall shown in Figure 13 on page 15 is to sample the back EMF at the correct point. The MP6602 samples the back EMF at the end of the zero-current step by default. This is useful for detection at continuous motion and fast speeds. To detect a stall at slow step rates, the sample point should be closer to the beginning of the zero-current step.

Detecting a "bouncing" stall at very low step rates is extremely difficult, as the bounces result in a similar back EMF as a normal step.

The point in time at which the back EMF is sampled can be configured via the BES1:BES0 bits in the CTRL2 register (see Table 7).

| BES1:BES0           | Back EMF Sample Point    |

|---------------------|--------------------------|

| 0x00                | 100µs after zero current |

| 0x01                | 200µs after zero current |

| 0x02                | 400µs after zero current |

| 0x03 <sup>(7)</sup> | End of zero current      |

Note:

7) Reset value.

#### Stall Detection Threshold Register Configuration (STH7:STH0)

A digital comparator monitors the back EMF A/D converter's output. If the back EMF drops below a configured threshold, this indicates a stall may have occurred.

The STH bits in the STALL register set the back EMF stall detection threshold. If the back EMF drops below the threshold, then the stall counter is incremented. If the back EMF exceeds the threshold, then the counter is decremented.

This threshold setting is a percentage of the back EMF A/D converter's full-scale output (which is also the BE7:BE0 bits).

| STH7:STH0           | Stall Detection Threshold<br>(% of Back EMF Voltage) |  |  |

|---------------------|------------------------------------------------------|--|--|

| 0x00                | No stall detected                                    |  |  |

| 0x01                | 0.4%                                                 |  |  |

| 0x02                | 0.8%                                                 |  |  |

|                     |                                                      |  |  |

| 0x7F                | 49.6%                                                |  |  |

| 0x80 <sup>(8)</sup> | 50%                                                  |  |  |

| 0x81                | 50.4%                                                |  |  |

|                     |                                                      |  |  |

| 0xFE                | 99.2%                                                |  |  |

| 0xFF                | 99.6%                                                |  |  |

#### Table 8: STALL Register Bit Settings for Different Stall Detection Thresholds

#### Note:

8) Reset value.

Finding the optimal STH bit settings is typically determined by testing different settings. Start at 50% of the maximum back EMF voltage (STH7:STH0 = 0x80), and move the threshold so that no false stall detections occur.

#### Stall Detection Count Register Configuration (SDT3:STD0)

The stall detect threshold comparator output is further processed by a counter to determine whether a stall has occurred. This prevents false reports of a stall due to dynamic mechanical conditions.

The STD bits in the STALL register set the number of steps that the stall counter should reach to report a stall condition. Table 9 shows the STALL register bit settings for the number of required to report a stall.

| STD3:STD0           | Steps Required to<br>Report a Stall |  |

|---------------------|-------------------------------------|--|

| 0x00 <sup>(9)</sup> | Stall detection<br>disabled         |  |

| 0x01                | 1                                   |  |

| 0x02                | 2                                   |  |

|                     |                                     |  |

| 0x0D                | 13                                  |  |

| 0x0E                | 14                                  |  |

| 0x0F                | 15                                  |  |

Note:

9) Reset value.

Finding the optimal STD bit settings is typically determined by testing different settings. A lower number may be required at low step rates (or if a bouncing stall is anticipated), since the bouncing can cause the back EMF to be captured while the motor is bouncing. The risk of too low a setting is that a stall might be falsely detected.

#### FAULT DETECTION AND CONFIGURATION

The MP6602 has a number of fault detection functions. These functions include open-load detection (OLD), over-current protection (OCP), over-temperature (OT) warning and OT shutdown, V<sub>IN</sub> overvoltage protection (OVP), VIN under-voltage protection (UVP), and VCC UVP .

If a fault occurs, a bit in the FAULT register is set to indicate the source of the fault. In most cases, the nFAULT pin is pulled active low. Fault conditions are cleared by writing a "1" to the appropriate bits in the FAULT register.

Table 10 shows a summary of the faults.

| Fault                                       | Device Action                                                                                   | Bits Set               | Bits Cleared By                     | nFAULT                                                                                    |  |  |  |  |

|---------------------------------------------|-------------------------------------------------------------------------------------------------|------------------------|-------------------------------------|-------------------------------------------------------------------------------------------|--|--|--|--|

| Over-current<br>(OC) fault                  | Outputs are latched off,<br>stepping is disabled                                                | OCPxx, OCP,<br>and FLT | Write "1" to OCP<br>(OCPxx cleared) | Active until OCP is<br>cleared                                                            |  |  |  |  |

| V <sub>IN</sub> over-voltage<br>(OV) fault  | Outputs and stepping are<br>disabled until V <sub>IN</sub> drops<br>below the its OVP threshold | OVP and FLT            | Write "1" to OVP                    | Active until OVP cleared                                                                  |  |  |  |  |

| V <sub>IN</sub> under-voltage<br>(UV) fault | Outputs and stepping are<br>disabled until V <sub>IN</sub> exceeds<br>the its OVP threshold     | VIUV and FLT           | Write "1" to VIUV                   | Active until V <sub>IN</sub><br>exceeds its under-<br>voltage lockout<br>(UVLO) threshold |  |  |  |  |

| VCC UV fault (10)                           | Device resets                                                                                   | VCCUV                  | Write "1" to VCCUV                  | Not active                                                                                |  |  |  |  |

| Over-temperature<br>(OT) warning            | No action                                                                                       | OTW and FLT            | Write "1" to OTW                    | Active until OTW is<br>cleared                                                            |  |  |  |  |

| OT shutdown                                 | Outputs are latched off,<br>stepping is disabled                                                | OTS and FLT            | Write "1" to OTS                    | Active until OTS is<br>cleared                                                            |  |  |  |  |

| Open-load fault                             | oad fault No action                                                                             |                        | Write "1" to OLx                    | Active until OLx is cleared                                                               |  |  |  |  |

| Stall No action                             |                                                                                                 | STALL, FLT             | Write "1" to STALL                  | Active until STALL is<br>cleared                                                          |  |  |  |  |

Table 10:

#### Note:

8/2/2022

10) If the device is reset, then VCCUV is set by either a start-up through VCC or the nRESET pin.

Refer to the MP6602 datasheet for more details.

#### **Over-Current Protection (OCP)**

If there is excessive amount of current flowing through any of the output pins, an over-current (OC) fault occurs. Four bits in the OCP register (OCPAH, OCPAL, OCPBH, and OCPBL) indicate whether the A or B output has experienced a fault, and whether the fault was sourcing (xxxxH, such as a short to ground) or sinking (xxxxL, such as a short to supply). A short across a motor winding can result in either one or both types of fault.

The OCP bit in the FAULT register is set, and the nFAULT pin is pulled low. To clear this fault, write "1" to the OCP bit. This also clears the OCPxx bits in the OCP register.

#### V<sub>IN</sub> Under-Voltage Protection (UVP), VCC UVP, and V<sub>IN</sub> Over-Voltage Protection (OVP)

The supply voltages are monitored. If the supply voltage are outside their normal operating ranges, then the part indicates that a fault has occurred.

VCC is the logic supply for the MP6602. If V<sub>CC</sub> drops below the VCC UVP threshold, then the IC logic is reset. If the logic is reset, then the registers return to their default values once the  $V_{CC}$  exceeds the threshold. This also sets the VCCUV bit. This does not pull nFAULT low. At start-up, this bit is set to indicate that the part has been reset. To clear this fault, write "1" to the VCCUV bit.

VCCUV is also set if the part is reset via the nRESET pin. VCCUV can be used as an indication to firmware that the registers have been cleared and should to be re-written.

$V_{IN}$  is also monitored for under-voltage (UV) faults. If  $V_{IN}$  drops below the  $V_{IN}$  under-voltage lockout (UVLO) threshold, then the device's outputs and stepping are disabled. The VINUV bit is set, and the nFAULT pin is pulled low. Depending on supply voltage sequencing, the VINUV bit may be set at power-up. This fault is cleared once  $V_{IN}$  exceeds the threshold, and a "1" is written to the VINUV bit.

If  $V_{IN}$  exceeds the  $V_{IN}$  OVP threshold, similar action is taken and the OVP bit is set. VIN overvoltage faults are cleared by lowering VIN and writing a '1' to OVP.

#### **Over-Temperature Warning (OT) and OT Shutdown**

A temperature sensor monitors the MP6602's die temperature. If the die temperature exceeds the OT warning threshold, then the OTW bit is set, and nFAULT is pulled low. No other action is taken. The fault is cleared once the temperature drops below the warning threshold, and a "1" is written to the OTW bit.

If the temperature exceeds the OT shutdown threshold, then the device's outputs and stepping are disabled. The OTS bit is set, and nFAULT is pulled low. The fault is cleared once the temperature drops below the threshold, and a "1" is written to the OTS bit.

#### **Open-Load Detection (OLD)**

The MP6602 can detect whether a motor winding is connected. This function is enabled by default, and can be disabled by setting the OLDIS bit to 1.

OLD works by checking whether the winding current has reached its target level. Open-load sensing is only performed at certain points in the step sequence, so it only detects whether the motor is being stepped.

OLD does not work at step rates above 1000 PPS. There is not enough time between steps to detect an open-load fault. In full-step mode, a false open load condition is detected if the current takes longer than 1ms to reach the current regulation set point. In this case, OLD should be disabled.

If an open load is detected, then the OLA or OLB bits are set. (The OLA and OLB bits correspond to the A and B outputs, respectively.) This fault condition is reset by writing a "1" to either OLA or OLB.

#### Stall Detection

If a stall is detected, then the STALL bit is set, and nFAULT is pulled low. This fault is cleared by writing a "1" to the STALL bit. If the motor remains in a stalled condition, then this bit can be set again.

#### Note:

11) Reset value.

# **REVISION HISTORY**

| Revision # | <b>Revision Date</b> | Description     | Pages Updated |

|------------|----------------------|-----------------|---------------|

| 1.0        | 8/2/2022             | Initial Release | -             |

**Notice:** The information in this document is subject to change without notice. Users should warrant and guarantee that thirdparty Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.